Research

We are a creative and energetic research group exploring interesting ideas in the design and synthesis of digital systems, especially in the programmable hardware realm.

Research Themes

Prof. Anderson's research relates to computer hardware design, and specifically to programmable logic devices such as field-programmable gate arrays (FPGAs) and coarse-grained reconfigurable arrays (CGRAs).

Dr. Anderson's work seeks to improve FPGAs and CGRAs from the area, speed, power and ease-of-use perspectives by innovations in circuits, architectures and tools. He is also interested in applications of such chips, particularly in area and power-constrained settings such as embedded systems. One of the application areas we are pursuing is implementing machine learning algorithms (artificial neural networks) on FPGAs to achieve higher energy effiency than standard processors.

Prof. Anderson's other research interests lie in computer-aided design (CAD) algorithms for integrated circuits, digital design and circuits, computer architecture and software engineering.

CGRA-ME: Coarse-grained configurable arrays/architectures (CGRAs) are programmable hardware devices with large ALU-like processing elements and datapath-style routing. They reside between FPGAs and custom ASICs on the spectrums of flexibility and power/performance efficiency. CGRA-ME is a modelling and exploration framework we are developing to enable new research on CGRA architectures and associated CAD tools. CGRA-ME is open-source and freely downloadable for non-commercial research purposes.

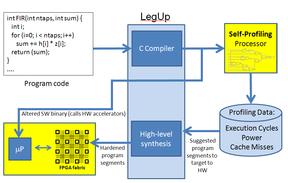

LegUp: An on-going project that aims to automatically compile C programs to processor/accelerator FPGA-based systems. The LegUp project is co-led by Profs. Anderson and Stephen Brown. Currently on its fourth public release, thousands researchers around the world have downloaded our high-level synthesis tool! Check out the LegUp research project website and try it out yourself! And, learn about the start-up company commercializing LegUp technology that was acquired by Microchip Technologies in October 2020!

Research Aims

We are attracted to research endeavours that align with three overarching criteria:

Novelty: We seek novel and innovative solutions to real problems, and prefer to be the first to break ground in new fields.

Accessibility: We pursue research that can be used and built-upon by others, that benefits the research community and the broader society, and that has low barriers to its practical application.

Impact: We aspire to produce results that are widely cited by other researchers, and we strive for excellence as recognized by our peers in the research community and in industry.

About Prof. Anderson

Jason Anderson is a Professor in

the Dept. of

Electrical and Computer

Engineering at the

University

of Toronto, where he holds the

Jeffrey Skoll Endowed Chair in

Software Engineering. He is

Director of

the minor

and certificate

programs in Artificial Intelligence

Engineering and is a Faculty

Affiliate of

the Vector

Institute for Artificial

Intelligence. His research

interests pertain to programmable

digital systems, particuarly, design

methodologies, architectures and

circuits for coarse-grained

reconfigurable arrays (CGRAs) and

field-programmable gate arrays

(FPGAs).

Jason Anderson is a Professor in

the Dept. of

Electrical and Computer

Engineering at the

University

of Toronto, where he holds the

Jeffrey Skoll Endowed Chair in

Software Engineering. He is

Director of

the minor

and certificate

programs in Artificial Intelligence

Engineering and is a Faculty

Affiliate of

the Vector

Institute for Artificial

Intelligence. His research

interests pertain to programmable

digital systems, particuarly, design

methodologies, architectures and

circuits for coarse-grained

reconfigurable arrays (CGRAs) and

field-programmable gate arrays

(FPGAs).

In 2019, Jason received the Faculty Teaching Award from the Faculty of Applied Science and Engineering. Dr. Anderson has received seven ECE departmental teaching awards for excellence in undergraduate teaching. In 2014, he received the Ontario Early Researcher Award from the Ministry of Research and Innovation. In 2013, he received the Faculty of Applied Science and Engineering Early Career Teaching Award. He has received five Best Paper Awards at international symposia. He is an inventor on over 30 U.S. patents, and he has co-authored over 100 research papers in refereed international journals and symposia, and 4 book chapters.

Prior to joining the university, Prof. Anderson spent 10 years at Xilinx, Inc., in California and Toronto, where he worked on the research and development (R&D) of automated synthesis tools and flows for Xilinx field-programmable gate arrays (FPGAs). In 2000, he received the Xilinx Ross Freeman Award for Technical Innovation: the top innovation award given by Xilinx. Prior to joining the UofT, he was a Principal Engineer and Manager at Xilinx, leading an R&D group with emphasis on improving tool run-time, FPGA speed, area and power-efficiency.

Jason was Program Co-Chair for the 2012 IEEE Int'l Conference on Field-Programmable Technology (FPT) held at Seoul, Korea. He was General Chair for the 2015 IEEE Int'l Symposium on Application-Specific Systems, Architectures, and Processors (ASAP) in Toronto, and for the 2018 Int'l Conference on Highly Efficiency Architectures and Reconfigurable Technologies (HEART). He was Program Co-Chair for FPL 2016 held at Lausanne, Switzerland and the Program Chair for FPGA 2017 held at Monterey, CA.

Dr. Anderson was an Associate Editor of IEEE Transactions on Circuits and Systems-II. He has also served as an Associate Editor for ACM Transactions on Design Automation of Electronic Systems (TODAES) and ACM Transactions on Reconfigurable Technology and Systems (TRETS). In his first sabbatical from 2014-2015, he was a visiting scholar at the Dept. of Electrical and Electronic Engineering at Imperial College London, UK, and also at the Dept. of Computer and Communications Engineering at Tokyo Institute of Technology, Japan as a Fellow of the Japan Society for the Promotion of Science. In his second sabbatical year (2022), he was a visiting professor at EPFL in Lausanne, Switzerland, and a Research Fellow at RIKEN in Kobe, Japan.

Prof. Anderson was

co-founder and Chief Scientific

Advisor

of LegUp

Computing Inc., a Toronto-based

start-up spawned from his group's

high-level synthesis research at the

University of Toronto. The start-up

was co-founded by his former

graduate students, Dr. Andrew Canis,

Dr. James Choi, and Lanny

Lian. LegUp computing was acquired by Microchip in October 2020.

Prof. Anderson was

co-founder and Chief Scientific

Advisor

of LegUp

Computing Inc., a Toronto-based

start-up spawned from his group's

high-level synthesis research at the

University of Toronto. The start-up

was co-founded by his former

graduate students, Dr. Andrew Canis,

Dr. James Choi, and Lanny

Lian. LegUp computing was acquired by Microchip in October 2020.

Jason did his graduate work (Ph.D. and M.A.Sc.) at the University of Toronto, and received his undergraduate degree from the University of Manitoba. He is a licensed Professional Engineer (P.Eng.) in the Province of Ontario, a Member of the ACM, and a Fellow of the IEEE.

Curriculum vitae (PDF)

Research Team

We are a vibrant and diverse team of researchers breaking new ground in the design of programmable digital hardware systems.

Ph.D. Students

Julie

(Hsuan) Hsiao joined the group in

September 2014, working on

reduced-precision high-level

synthesis. She spent her

professional experience year at

Qualcomm in Toronto. During her

graduate studides, she interned at

IBM T.J. Watson Lab in Yorktown

Heights, NY. She completed her

M.A.Sc. in 2017.

Julie

(Hsuan) Hsiao joined the group in

September 2014, working on

reduced-precision high-level

synthesis. She spent her

professional experience year at

Qualcomm in Toronto. During her

graduate studides, she interned at

IBM T.J. Watson Lab in Yorktown

Heights, NY. She completed her

M.A.Sc. in 2017.

Rami Beidas joined the group in January 2020, resuming his Ph.D. studies after several years of working at a startup in industry. Rami has made a number of research contributions in high-level synthesis and is currently working on applications of zero-suppressed binary decision diagrams (ZDDs) to CGRA CAD.

Adham Ragab joined

the group in September 2024 as a

Ph.D. student. He has been

researching CAD techniques for

CGRAs.

Adham Ragab joined

the group in September 2024 as a

Ph.D. student. He has been

researching CAD techniques for

CGRAs.

M.A.Sc. and M.Eng.-Project Students

Lancy Wang

completed her undergraduate degree

in Engineering Science at UofT with

a PEY at Marvell. She interned with

our group in the summer of 2020,

working on multi-pumping CGRA

interconnect. She is working on CGRA

architecture. She interned at RIKEN

in Kobe, Japan in the summer of

2023.

Lancy Wang

completed her undergraduate degree

in Engineering Science at UofT with

a PEY at Marvell. She interned with

our group in the summer of 2020,

working on multi-pumping CGRA

interconnect. She is working on CGRA

architecture. She interned at RIKEN

in Kobe, Japan in the summer of

2023.

Hamas Waqar joined the group in

the fall of 2023. He is researching

CGRA mapping and network-on-chip

(NoC)/CGRA integration.

Hamas Waqar joined the group in

the fall of 2023. He is researching

CGRA mapping and network-on-chip

(NoC)/CGRA integration.

Omkar Bhilare joined the group

in the fall of 2023. He is

researching CGRA mapping and

network-on-chip (NoC)/CGRA

integration.

Omkar Bhilare joined the group

in the fall of 2023. He is

researching CGRA mapping and

network-on-chip (NoC)/CGRA

integration.

Lily Li joined the group in September 2024 as an M.A.Sc. student.

Sebastian Czyrny joined the group in September 2024 as an M.A.Sc. student.

Group Alumni

Visiting Faculty

Takahiro Notsu was a visiting researcher from Fujitsu Laboratories in Kawasaki, Japan, visiting us for a year from October 2019. Taka worked on machine-learning applications in CAD and contributed to our CGRA-ME project.

Prof. Jongeun Lee visited us from Ulsan National Institute of Science and Technology (UNIST), South Korea, from 2017-2018. Prof. Lee's research interests include machine learning, reconfigurable processors, application-specific processors, and compilation for low power, reliability, and multi-core processors.

Graduate

James Liu completed

his M.A.Sc. in 2024 working on CGRA

architecture. He specifically

researched automated approaches for

reconfigurable processing element

design.

James Liu completed

his M.A.Sc. in 2024 working on CGRA

architecture. He specifically

researched automated approaches for

reconfigurable processing element

design.

Salim Khemira

completed his M.A.Sc. in 2025. His

research was on approximate

computing for molecular dynamics

simulations via memoization.

Salim Khemira

completed his M.A.Sc. in 2025. His

research was on approximate

computing for molecular dynamics

simulations via memoization.

Stephen Wicklund

joined the group in 2022 and

completed his M.A.Sc. in 2025. He

worked on MLIR-based compilation for

CGRAs and interned at Riken in

summer of 2024. He joined Fujitsu

on graduation.

Stephen Wicklund

joined the group in 2022 and

completed his M.A.Sc. in 2025. He

worked on MLIR-based compilation for

CGRAs and interned at Riken in

summer of 2024. He joined Fujitsu

on graduation.

Haoran Wei was an M.Eng. project student who worked on linking CGRAs with a network-on-chip (NoC). He graduated in 2024.

Aditya Srichandan was an M.Eng. project student who worked on implementing systolic arrays on CGRAs. He graduated in 2025.

Dr. Omar Ragheb

completed his Ph.D. in 2025. He

worked on CAD and architecture for

CGRAs, particularly elastic CGRAs.

He joined Fujitsu upon graduation.

Dr. Omar Ragheb

completed his Ph.D. in 2025. He

worked on CAD and architecture for

CGRAs, particularly elastic CGRAs.

He joined Fujitsu upon graduation.

Linda Yu was a

master's student who joined the team

in the summer of 2020. She

contributed to the CGRA-ME project,

specifically high-level compilation

using MLIR to CGRAs. Linda completed

her Professional Experience Year at

Flipp in Toronto. She joined

AMD/Xilinx upon graduation.

Linda Yu was a

master's student who joined the team

in the summer of 2020. She

contributed to the CGRA-ME project,

specifically high-level compilation

using MLIR to CGRAs. Linda completed

her Professional Experience Year at

Flipp in Toronto. She joined

AMD/Xilinx upon graduation.

Gabriel (Guanglei)

Zhou joined the group in 2020 after

completing his undergraduate degree

at the City University of Hong Kong.

He spent a semester during his

undergraduate studies as an exchange

student at UofT. He worked on CGRA

mapping and also reinforcement

learning in logic synthesis. He

graduated in 2022 and is currently a

Ph.D. student at Duke

University.

Gabriel (Guanglei)

Zhou joined the group in 2020 after

completing his undergraduate degree

at the City University of Hong Kong.

He spent a semester during his

undergraduate studies as an exchange

student at UofT. He worked on CGRA

mapping and also reinforcement

learning in logic synthesis. He

graduated in 2022 and is currently a

Ph.D. student at Duke

University.

Dr. Jin Hee Kim joined the group in September 2013. She completed her B.A.Sc. at Toronto, spent a year on overseas study in the UK, and interned for a year at Microsemi/Actel in the Bay Area. For her M.A.Sc. studies, she researched standard-cell implementations of FPGA fabrics. Jin Hee commenced her Ph.D. studies in September 2015, working on FPGA architecture and CAD, and machine-learning acceleration. She interned at Samsung USA in summer 2016 and joined Intel upon her graduation in 2021.

Austin Liolli joined the group in September 2018 and graduated in 2021. His research pertained to control-flow elimination and predication, applied in high-level synthesis. He completed his undergraduate studies at the University of Windsor. He joined Ford Motor Company upon graduation.

Shirley Xiaoyi Ling joined the group in January 2020 contributing to the CGRA-ME project, graduating in fall 2021. She specifically worked on integrating CGRAs with a RISC-V processor. She completed her undergraduate degree at the University of Washington, Seattle, WA. She joined Sunnybrook Hospital research upon graduation.

Vimal Varghese Chacko joined the group in January 2020 contributing to the CGRA-ME project. His research pertained to multi-context CGRAs. He completed his undergraduate degree at Model Engineering College, India. He then worked in industry for three years at National Instruments and ANSYS, before commencing his graduate studies at Toronto. He joined Intel Corp. upon graduation.

David Ma worked with us for the summer of 2020, contributing to the CGRA-ME project on latency insensitive CGRAs. He completed his M.Eng. degree in 2020. He joined LegUp Computing upon graduation.

Ian Taras joined the group in September 2017. He completed his undergraduate studies at the University of Western Ontario. He interned at ISI in the summer of 2019, and he completed his M.A.Sc., on FPGA-overlay CGRAs, in 2020.

Nicholas Giamblanco joined the group in September 2017. He completed his undergraduate studies at Ryerson University. He interned at ISI in the summer of 2019, and he completed his M.A.Sc., on dynamic memory allocation supportin HLS, in 2020.

Daichi Teruya was a visiting Ph.D. student from the Tokyo University of Agriculture and Technology, Japan, from June - November 2019. He researched approaches for supporting function pointers in high-level synthesis.

Brett Grady joined the group in June 2016. He received his bachelor's degree from Ryerson University and interned at AMD during his undergraduate studies. His M.A.Sc. research, completed in 2018, was on synthesizable standard-cell FPGAs. During his M.A.Sc., he interned at Intel Research, Santa Clara, CA. He is currently with Efinix in Toronto.

Joy (Yu Ting) Chen joined the group in September 2014, working on memory architecture synthesis within high-level synthesis. She completed her M.A.Sc. in 2017. She spent her professional experience year at AMD in Toronto. During her graduate studies, she interned at Intel in Hudson, MA. She is currently with Tenstorrent in Toronto.

Matthew Walker joined the group in September 2017. He completed his undergraduate studies at the University of Toronto and spent his Professional Experience Year at Altera/Intel in Toronto. He worked on mapping techniques for CGRAs and graduated in 2019. He is currenty with Tenstorrent in Toronto.

Steven Niu joined the group in September 2016. He's an alumni of U of T's ECE department and has been working in Toronto-based start-up companies for the past several years. After finishing his M.A.Sc. in early 2019, he joined Xilinx, Inc., in Beijing, Ching.

Dr. Xander Chin joined the group in September 2012, after having spent 6 months working at Xilinx in San Jose, CA. Prior to that, Xander completed his M.A.Sc. thesis on memory subsystem architecture working with Professor Paul Chow. For his PhD research, Xander worked on hybrid logic element architectures for FPGAs, and on architecture evaluation of coarse-grained reconfigurable arrays (CGRAs), and he launched the CGRA-ME project. He graduated in 2018.

Dr. Safeen Huda completed his Ph.D. in 2017 with a dissertation on low-power FPGA architcture, circuits and tools. During the spring of 2015, he interned at Efinix, an FPGA start-up in the Bay Area. He completed his M.A.Sc. under the supervision of Prof. Ali Sheikholeslami, working in the area of spintronics. Safeen did his B.A.Sc. project research on clock gating architectures for FPGA power reduction.

Dr. James (Jongsok) Choi contributed to the LegUp high-level synthesis project, working on the Pthreads/OpenMP flow. His M.A.Sc. thesis focussed on automated hardware/software co-design. He received his B.A.Sc. from the University of Waterloo, and interned previously at Qualcomm, Marvell Semiconductor, RIM and Genesis Microchip (now STMicro). He was co-supervised by Prof. Stephen Brown.

Lanny Lian joined the group in September 2013, having also been with us for the summer of 2012. He worked on an FPGA implementation of machine learning (deep neural network). Lanny completed his B.A.Sc. at Toronto and interned for a year at Altera in San Jose, CA, and in Fall 2014 interned at Google. He completed his M.A.Sc. in 2016 and is now working on commercializing LegUp HLS.

Dr. Andrew Canis completed his PhD in 2015 on high-level synthesis for FPGAs and is a primary contributor to the LegUp open-source HLS project. Andrew is a graduate of the University of Waterloo's ECE program and completed internships at Altera, Sun Microsystems, and Oracle. He was co-supervised by Prof. Stephen Brown. He is working on commercializing LegUp HLS.

Dr. Charles Eric LaForest worked on "how FPGAs want to compute", specifically, on the design of FPGA soft processors capable of operating in the 500MHz range. He was co-supervised by Prof. Greg Steffan and joined AMD in Toronto upon graduation.

Dr. Jason Luu completed his Ph.D. in 2014, working on generic packing techniques and block architectures for FPGAs. He attended the University of Waterloo for his undergraduate studies. Jason was co-supervised by Prof. Jonathan Rose and joined Altera in Toronto upon graduation.

Nazanin Calagar joined the group in September 2012, co-supervised by Prof. Stephen Brown, and received her M.A.Sc. in 2014. She worked on debugging approaches for high-level synthesis. She received her bachelor's degree from Shahid Beheshti University, Iran, and she joined Microsoft in Seattle, WA upon graduation..

Steven Gurfinkel joined the group in summer 2011 and graduated in 2013. He worked on heterogenous GPU/CPU computing. He was co-supervised by Prof. Natalie Enright Jerger and joined NVIDIA upon graduation in Santa Clara, CA, USA.

Dr. Marcel Gort joined the group in September 2009 and completed his Ph.D. in 2013. He received the B.Eng. in Computer Engineering from the University of Western Ontario, with an internship at the IBM Toronto Software Lab from May of 2005 to August of 2006 as part of the compiler group. He completed his M.A.Sc. at the University of British Columbia under the supervision of Dr. Steve Wilton. For his Ph.D. research, he worked on fast CAD for FPGAs. He joined Altera upon graduation.

Tahir Diop joined the group in September 2011 and graduated in 2013, joining TXIO -- a Toronto start-up. His thesis was on distributed OpenCL execution and power modeling for heterogeneous GPU/processor architectures. He completed his undergraduate degree in Computer Engineering at the University of Manitoba.

Bill Teng researched latch-based techniques for FPGA performance improvement. He graduated from U of T's ECE program with honours in 2008. He has worked at Cognos (now IBM) and Nortel as a Software Engineer. Bill's academic interests are VLSI, algorithms, computer architecture, and parallel programming. He joined Achronix Semiconductor upon graduation with his M.A.Sc.

Warren Shum worked on synthesis techniques for FPGA power reduction and also on algorithmic noise analysis/mitigation in FPGA CAD. He received the B.A.Sc degree in ECE from U of T in 2009 with a minor in bioengineering. From 2007-2008, Warren worked at Altera Corporation, in the power modelling group. In his spare time, Warren enjoys playing, composing, and listening to music. He joined Altera upon graduation with his M.A.Sc.

Mark Aldham was an M.A.Sc. student researching embedded processors and automatic hardware profiling. He is a graduate of UofT's Engineering Science program. He graduated in 2011 with his M.A.Sc., and joined Microsoft in Redmond, Washington, USA. He was co-supervised by Prof. Stephen Brown.

Edgar Mora-Sanchez was an M.Eng. student researching stochastic computing and probabilistic circuits implemented in FPGAs. He is currently working at Intel in Austin, TX.

Noriaki (Nori) Sakamoto visited us from Tokyo Institute of Technology, where he worked with Prof. Yuko Hara-Azumi, on light-weight processor architectures and tools. He visited us in summer 2015 and worked on architecture description for coarse-grained reconfigurable arrays.

Yuta Otsuka visited us from 2016-2017. He was a graduate student working with Prof. Kentaro Sano at Tohoku University in Sendai, Japan.

Undergraduate Summer Interns

Angus Wu, Evan Chen, Adham Ragab, Dylan Sun, Lancy Wang, Cassie Li, Kath Choi, Zeng Zeng, Louis He, Graham Hoyes, Tristan Chen, Justin Hai, Samridhi Bansal, Zak Georgis-Yap, Alex Mertens, Ali Nickooie, Steven Yin, Fan Xie, Allan Rui, Dhruv Chawla, James Jin, Mathew Hall, Jim Zhao, Jenny Deng, Yvonne Zhang, William Cai, Emily Miao, Yolanda Wang, Ana Klimovic, Lanny Lian, Jenny Huang Qijing, Ryan Xi , Miad Nasr, Kevin Nam, Stefan Hadjis, Alex Liu, Ahmed Kammoona, Victor Zhang, Chirag Ravishankar

Recent Team Outings

October 2021: Clockwise from left: Jason, Gabriel, Vimal, James, Lancy, Jin Hee, Linda, Alex (guest), Omar (cut off), Salim, Manling (guest), Shirley. Missing: Rami and Julie

November 2019: Clockwise from left: Omar, Zeng, Austin, Ian, Daichi, Louis, Taka, Jason, Jin Hee, Tyler, Nick, Jen, Julie

News

Latest news and accolaides about the research team.

December 2022: Prof. Anderson has been elevated to IEEE Fellow, class of 2023, "for contributions to high-level synthesis and low-power FPGAs".

November 2022: Congrats to Gabriel on his accepted IEEE/ACM ASP-DAC 2023 paper. "Area-driven FPGA Logic Synthesis Using Reinforcement Learning," Zhou and Anderson. ASP-DAC will be held at Tokyo in January 2023.

August 2022: Congrats to Omar, Linda and David on their accepted FPL 2022 paper! "Modeling and Exploration of Elastic CGRAs," Ragheb, Yu, Ma, Anderson. FPL will be held at Belfast Ireland in August!

March 2022: Congrats to Omar, Linda and Rami on their paper accepted to the First Int'l Workshop on CGRAs for High-Performance Computing (CGRA4HPC) to be held in conjunction with IPDPS. ``Elastic Multi-Context CGRAs," Ragheb, Yu, Beidas, Anderson. Workshop website.

November 2021: Calling all CGRA researchers! Am excited to announce that the first International Workshop on Coarse-Grained Reconfigurable Architectures for High-Performance Computing (CGRA4HPC) will be held in conjunction with IPDPS 2022 in Lyon, France, May 2022. Paper submissions are due January 26, 2022 and accepted papers will be submitted for inclusion in IEEE Xplore. For more information and the Call for Papers, visit the workshop website.

October 2021: Congrats to Austin and Omar and their paper accepted to the 2021 IEEE Int'l Conf. on Field-Programmable Technology (FPT)! "Profiling-Based Control-Flow Reduction in High-Level Synthesis," Liolli, Ragheb, Anderson.

Contact

Mailing Address:

Dept. of ECE, University of Toronto, 10 King's College Road, Toronto, ON M5S 3G4 CANADA

Office Address:

Engineering Annex, Room 314 (EA314), 11 King's College Road

Email:

janders@ece.utoronto.ca

Call:

+1 416 946-7285